您现在的位置是:首页 > 电路图 > 电路图学习 > 电路图学习

FPGA开发外设子板模块电路设计详解 —电路图天天读(161)

![]() 转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-08-18

转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-08-18

简介FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,

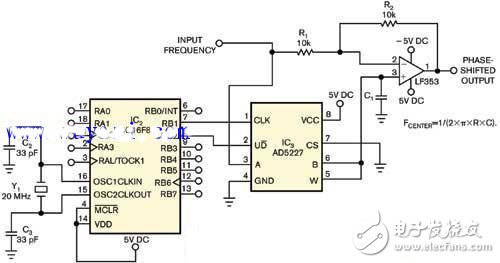

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA的开发相对于传统PC、单片机的开发有很大不同。FPGA以并行运算为主,以硬件描述语言来实现;相比于PC或单片机(无论是冯诺依曼结构还是哈佛结构)的顺序操作有很大区别,也造成了FPGA开发入门较难。目前国内有专业的FPGA外协开发厂家,开发展基本电路如下:

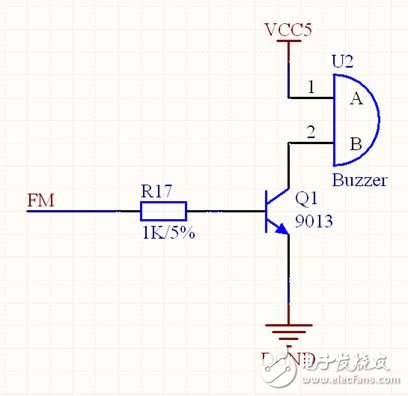

蜂鸣器电路如图3.47所示。FM信号由FPGA的I/O口控制。当FM为高电平时,Q1的BE导通,则CE导通,蜂鸣器的5V和GND形成回路,发出声音。当FM为低电平时,Q1的BE断开,则CE断开,蜂鸣器的5V和GND断开,因此没有电流流过蜂鸣器,蜂鸣器便不发声。在后面的实验中,我们可以使用PWM信号,即以固定的时高时低的电平控制Q1的导通与否,然后达到蜂鸣器的时断时开,人耳听到的便是不同频率的声响。

图3.47 蜂鸣器驱动电路

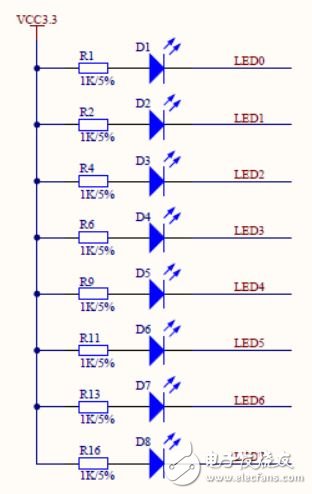

8个LED指示灯的电路如图3.48所示,他们公共端接电源3.3V,另一端连接FPGA的I/O口。若输出高电平,LED熄灭;若输出低电平,则LED点亮。这8个LED的接口是与数码管的段选信号复用的。

图3.48 8个LED指示灯电路

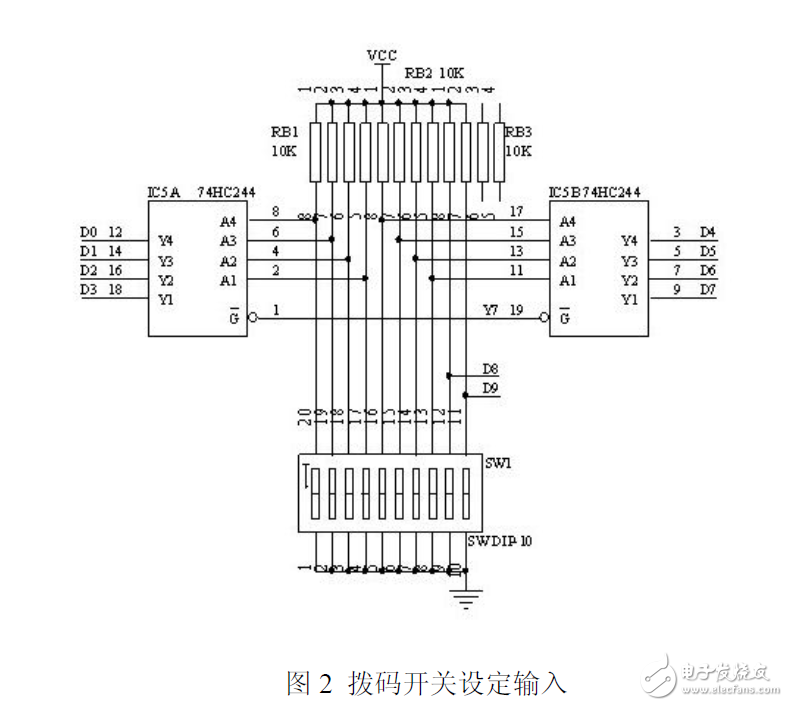

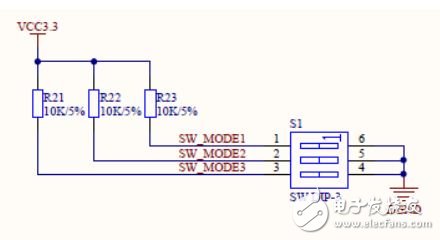

3位的拨码开关电路如图3.49所示。

图3.49 拨码开关电路

如图3.50,我们可以对照实物,默认3个拨码开关应该都是拨向左侧(即1、2、3标记侧),在电路图上就是VCC3.3上拉一侧。就是说,默认情况下,3个连接FPGA的I/O口的信号SW_MODE1、SW_MODE2、SW_MODE3均为高电平。若拨码开关被拨到右侧(即标记ON侧),则采集到的输入就是低电平了。

图3.50 拨码开关实物照片

12下一页全文本文导航

- 第 1 页:FPGA开发外设子板模块电路设计详解 —电路图天天读(161)

- 第 2 页:数码管驱动电路详解