您现在的位置是:首页 > 电路图 > 电路图学习 > 电路图学习

FPGA数码相框电子电路设计大全 —电路图天天读(101)

![]() 转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-08-18

转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-08-18

简介随着社会经济的发展和生活物质水平的提高,人们对于精神世界的追求也越来越高。该设计理念源于提高人们的生活幸福指数。在传统意义上,人们往往用冲印出来的相片来记录生活中

随着社会经济的发展和生活物质水平的提高,人们对于精神世界的追求也越来越高。该设计理念源于提高人们的生活幸福指数。在传统意义上,人们往往用冲印出来的相片来记录生活中的美好瞬间。然而伴随电子行业的发展,包括数码相机,高像素智能内的大量电子产品大行其道,足以用数码形式将其取代。据统计,世界上那个70%以上照片都是数码照片,年轻一族更是喜欢以数码形式记录他们的生活,并且分享在网络上。数码相框同时还可以将静态图片提升为动态的相册,携带方便,储存时间长远,满足于人们的需求,同时也会是一种节约型,环保低碳型的构想。

FPGA 工作原理

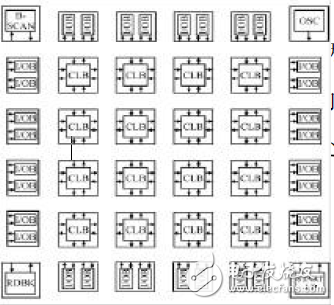

一个典型的FPGA 是有几个部分构成的,首先是逻辑块(LogicBlock),Altera 公司将其称之为逻辑阵列快(LAB)Xilinx 公司将其称为可配置逻辑块(CLB)。LAB 由称之为LE(Logic Element)的基本单元构成,CLB 由称之为LC(Logic Cell)的基本单元构成。这些就是FPGA 的逻辑资源,还有一部分是散落在各个逻辑块之间地内部连线,它们好比是PCB 板上的导线,将FPGA 内部地各个逻辑相连接,起点和终点都是IOB(I/O Block)。另一部分就是IOB 了,IOB 是FPGA的外部物理接口,类似IC 的各引脚,当然这里是根据用户需要自己可以任意定义的。如今的FPGA 的IOB 已经很强大, 从基本的LVTTL/LVCOMS 接口到PCI/LVDS/RSDS 甚至各种各样的差分接口,FPGA内部的I/O 实际上是分组的,但是每一组都可以灵活配置,改变上拉下拉电阻,调解驱动电流大小,兼容5V,3.3V,2.5V,1.8V 甚至1.5V,可以满足不同的电器特性,不同的I/O 接口物理特性以及外部硬件电路对输入输出信号的各种匹配要求。目前I/O 可以达到的频率也愈来愈高,通过特定的技术数据读取速率甚至可以达到2Gbps 现在越来越多的工程师喜欢FPGA,强大的I/O 特性也是一种原因吧。

图2-1 典型的FPGA内部结构图

I/O 兼容恐怕是大势所趋。设计IOB 的概念和技术还有很多,这里不做介绍了。还有一部分就是FPGA 内部的功能模块,是制造商根据实际需要放置在FPGA 内部的。比如数字时钟管理模块即DCM,Xilinx 公司的FPGA 全都具有这种功能。比如相位环路锁定。PLL 需要一个外部时钟输入(晶振),经过内部处理后(包括分频和倍频)可以提供在频率和相位上都比较稳定的一定范围内的时钟。还有不得不提的内部不占用逻辑资源的块RAM。RAM 块可用作为单口RAM、双口RAM、内容地址存储器以及FIFO(first in first out)等常用存储器甚至ROM,移位寄存器。这对于小量数据缓存很有用,强化了FPGA的应用性。在选择FPGA 时,芯片内部块RAM 的资源多少也是衡量的一个重要因素。单独块RAM 的容量为18kbit 宽为18Bit、深度为1024,可以根据实际需要改变其位宽和深度,但有两点限制:首先就是修改后块RAM 的容量(位宽深度)不能大于单片块RAM 容量;而且位宽最大不能超过36Bit,可以将多片块RAM 联起来形成内存更大的RAM,此时只受限于芯片内块RAM 的数量,而不再受上面两条原则约束。不过在Quartus 中,具体操作起来很方便。还有底层内嵌功能单元包括内嵌专用硬核如乘法器等。它对于数字信号的运算处理提供极大的便利。

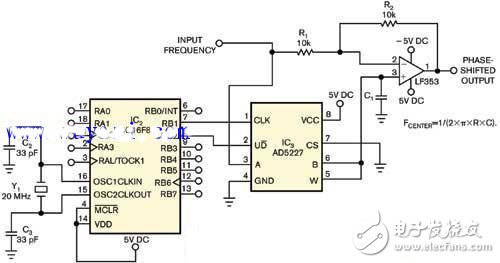

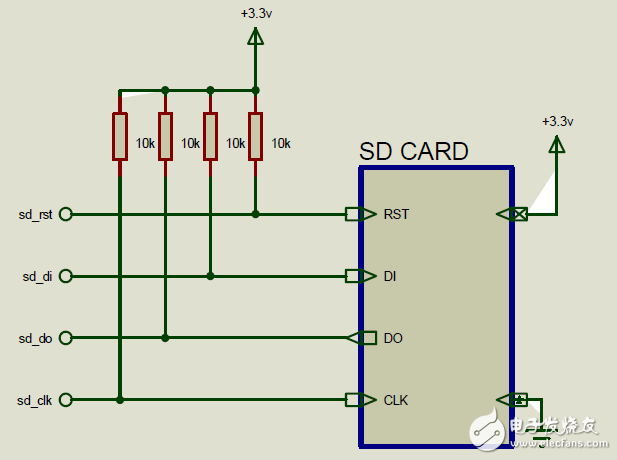

SPI 接口控制电路

图4-1 SPI模式连接图

该工程模块的SPI 接口四条信号线分别定spi_cs_n,spi_clk,spi_miso 和spi_mosi。其中spi_cs_n 是数据控制使能信号,当要对芯片进行操作时,此信号低电平有效。也就是说在同一条主线上可以连接多个SPI。spi_clk是SPI 同步时钟信号,数据信号在该时钟的控制下进行逐位传输。spi_miso 和spi_mosi 是主从机进行通信的数据信号,spi_miso即主机的输入或者说是从机的输出spi_mosi 即主机的输出或者说是从机的输入。

本文导航

- 第 1 页:FPGA数码相框电子电路设计大全 —电路图天天读(101)

- 第 2 页:VGA 显示驱动模块电路设计