您现在的位置是:首页 > 电路图 > 电机控制电路 > 电机控制电路

四路串行CMOS复接器的设计实现

![]() 转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

简介阮峥,陈亮,王宝瑛 (公安部第三研究所,上海 201204) 摘要:通信系统中,数字复接是提高带宽利用率的一项重要技术,将多路并行低速信号转变为高比特率的串行数字流。首先使用

阮峥,陈亮,王宝瑛

(公安部第三研究所,上海 201204)

摘要:通信系统中,数字复接是提高带宽利用率的一项重要技术,将多路并行低速信号转变为高比特率的串行数字流。首先使用Cadence软件仿真基本门级CMOS电路,通过自下而上的FPGA设计方法和Verilog硬件描述语言,设计四路串行复接器的功能组成模块,完成Quartus II平台上的可综合验证。最后提出了复接器CMOS集成电路的设计思路。

关键词:门级电路;Verilog;Quartus II;复接器;CMOS集成电路

0引言

通信系统中,一路独立信号的速率通常都是较低的,通信设备的带宽却相对较大。多路复用技术正是解决信源速率与传输带宽之间不对称问题的有效途径之一,通常使用频分复用、时分复用、波分复用和码分复用四种复用系统。基于时分复用理论的复接器,按照时序依次将N路相同速率和相位的低速信号整合为一路N倍速率的高速信号,以提高传输物理介质带宽的利用率。随着电路制作工艺的不断进步,复接器系统可以由多种基本复接电路组合,来实现Gb/s级别的工作速率,因而普遍用于通信系统的信道接口部分[1]。

集成电路设计之前一般需要经过现场可编辑逻辑阵列(FPGA)的功能验证。作为一种通用半定制电路,FPGA的硬件验证可以方便在电路设计的早期发现问题,达到降低研发费用、缩短开发周期的效果,因此对芯片的逻辑综合和版图设计具有重要意义。

本文在4∶1串行复接器的经典设计原理基础上,介绍基本门级CMOS电路的仿真,并在Quartus下设计验证复接器各组成电路模块,分析电路时序逻辑功能。

1基本门级电路的CMOS设计仿真

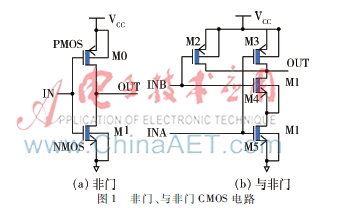

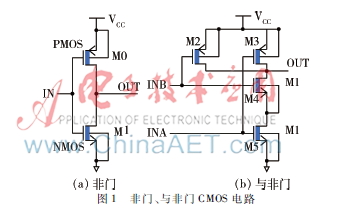

基本非门和与非门的CMOS电路如图1所示。

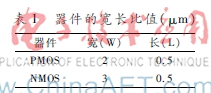

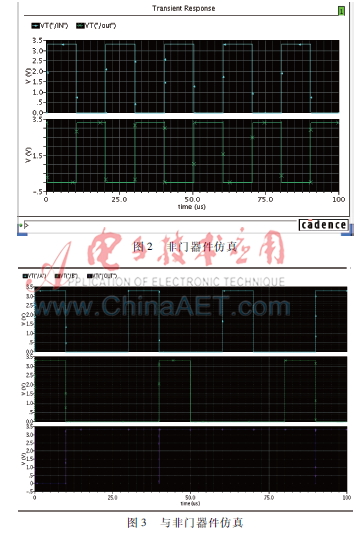

PMOS管和NMOS管的两个栅极相连作为输入,各自的漏极相连作为输出,当输入信号IN大于NMOS的阈值电压时,M1导通,PMOS管截止,输出信号OUT接地,为低电平输出;当IN低于阈值电压时,M0导通,M1截止,输出信号OUT与VCC形成通路,输出高电平,这样就构成了图1所示的非门,又称反相器。两个PMOS管并联后再与两个串联的NMOS管相连,构成二输入的与非门。当输入INA和INB其中一个或者全都为低电平,M3、M2中的一个或全部导通,输出信号OUT与高电平VCC形成通路,输出高电平;当且仅当输入全为高电平时,M1、M2导通,输出信号OUT直接接地,输出低电平,构成图1所示的与非门电路[2]。借助Cadence软件,按照表1给出的参数设置器件的宽长值,对非门、与非门进行器件仿真。表1器件的宽长比值(μm) 器件宽(W)长(L)PMOS20.5NMOS30.5器件仿真的结果如图2、图3所示,可以看出符合相应器件的逻辑特性。

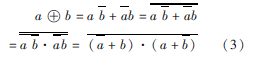

图5四路串行复接器原理图其他基本门电路逻辑如公式(1)~(3)所示:

式中a、b表示二输入逻辑门的输入信号。

公式表明,或门、异或门等基本电路都可以由与门、与非门构成,称之为基本CMOS逻辑门电路。基本门级电路继续构成多种形式和驱动能力的触发器、多路器、缓冲器等基本电路单元,并且作为集成电路制造厂家的标准单元库,提供给设计人员使用。需求电路的逻辑设计验证后,再进行电路的版图设计、验证、后仿真、流片、测试,最终在管级器件上实现[3]。

2复接原理

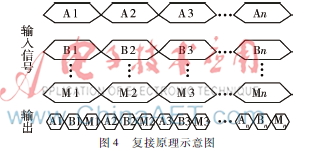

数字复接的作用是将低速数据码流变换成高速数据码流的设备[4]。图4为M路信号的复接示意图,M路信号在时序控制电路作用下,由时钟信号控制时序,有条不紊地复接每一路独立信源,依次输出复接信号,其实质是在抽样时间内传输一路数据,在其他时隙用于传输其他路信源数据。

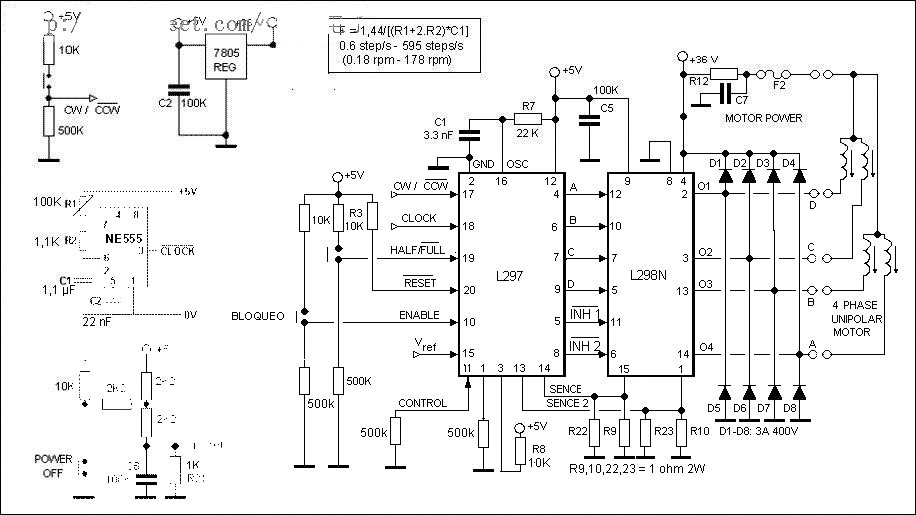

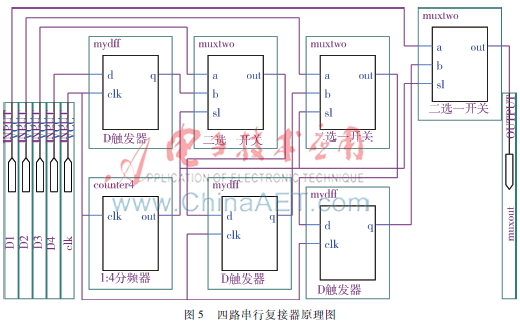

4∶1串行复接器电路系统由三个D触发器、三个2∶1的通道选择器以及一个1:4分频器构成[5],如图5所示。D触发器用于数据锁存,通道选择器作为单刀双掷开关。时钟信号上升沿触发触发器,锁存前端选择器的输出比特。分频信号触发通道选择,高电平选择信号a,低电平选择信号b。如分频信号正向脉冲期间,数据D1的一个比特直接输出,而时钟信号上升沿将数据D2,D3,D4的比特锁存在相应的D触发器中,直到分频信号负向脉冲到来移出,这样D1、D2、D3、D4的数据一位接一位地输出,表现为数据的复接。

数据复接的条件如下:

(1)需要复接的数据在一个分频时钟周期内保持稳定。

(2)时钟信号的上升沿触发锁存,通道选择器高电平输入选择信号a,低电平输入选信号b。

(3)分频器输出占空比必须为1∶3。

在CK/4信号的正向脉冲期间,D触发器和选择器组成了一个移位寄存器。存储的数据D2、D3和D4一位接一位输出。任何占空比的分频器都可以通过硬件描述语言实现[6]。电路用到两个时钟信号:频率等于复接器输出比特率的时钟信号和只有输出频率1/4的分频信号,前者用于数据寄存,后者用于数据移位,低速时实现相对容易。随着输出速率提高以及复接信号源数目的增加,D触发器的速率可能限制整个电路的输出速率,同时通道选择器在一个输出比特的周期内要完成信号的选择,需要的速度也必须很高,功耗的问题也会表现出来,因为所有D触发器都工作在最高频率的时钟信号上,而CMOS管的功耗与翻转频率成正比。

这种结构的电路运行速度取决于n级移位寄存器和时钟通道的第一级分频器。D触发器的速度有可能限制分接器的速度,因为整个移位寄存器链路和分频器的第一级中的D触发器的频率必须等于输出的速度。另外,所有通道选择器的速度也必须很高,因为它们在一个输出数据比特周期内必须完成选择的功能。因此,电路设计所用的技术是非常关键的,因为所有移位寄存器都是主从触发器,为达到高速,通道选择器也需要大电流。这样功耗就会很高。

3程序设计

3.1触发器的设计

时钟信号上升沿时刻,寄存并输出信号源。可综合Verilog代码片段如下:

always @(posedge clk)

begin

q<=d;

end

3.2二选一电路的设计

根据输入信号电平的高低,决定输出选择信号的二选一电路模块的代码片段如下:

always@(sl or a or b)

if(sl)

out<=a;

else

out<=b;

3.3分频器电路的设计

分频器电路可以借助状态机、计数器两种基本方法,根据不同的占空比要求来选择。这里采用计数器原理来实现占空比为1∶3的分频器设计,代码片段如下:

always @(posedge clk)

if(count==2'b00)

out<=1;

count<=count+1;

else

out<=0;

if(count==2'b11)

count<=2'b00;

else

count<=count+1;

4结论

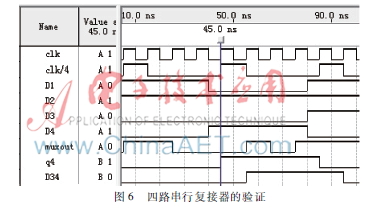

电路模块各自得到Quartus II仿真验证后,由当前文件形成各自symbol文件,用于完成复接器工程原理图的自下而上的设计。复接器中所有的过程信号都以管脚信号输出,用以显示功能验证的正确性。

截取的功能仿真结果如图6所示。仿真中添加了图5电路中以D4作为输入信号的触发器的输出信号q4、以D3作为输入信号a的二选一电路的输出D34和分频器的输出信号clk/4。可以看到,时钟信号clk的周期为10 ns,分频后输出信号的周期为40 ns,频率为时钟信号的1/4,占空比为1∶3。q4在时钟上升沿锁存D4信号,与其电平保持一致。D34在分频信号为高电平时刻选择信号D3,低电平时刻选择信号D4。在第一个时隙(5 ns~45 ns)内,D1~D4输入数据依次为1,1,0,0,这一时期的输出复接信号muxout为1100,达到信号复接要求;第二个时隙(45 ns~85 ns)内D1~D4输入数据依次为0,1,0,1,其间输出复接信号muxout为0101,满足信号复接要求;后续时隙仿真功能依然正确。经可综合风格的硬件描述语言验证的电路,再通过集成电路设计专用工具,逻辑综合成逻辑门电路网表,由CMOS标准单元库最终完成复接器集成电路的设计制造。

参考文献

[1] 杨洋. 0.6umCMOS 4:1高速复接器设计[D]. 合肥:合肥工业大学,2007.

[2] 凌云. 高速复接器设计[M].南京:东南大学出版社,2006.

[3] 王志功,景为平,孙玲. 集成电路设计技术与工具[M]. 南京:东南大学出版社,2007.

[4] 赵怡,但涛. 基于FPGA的多路数字信号复接系统设计与实现[J].电子科技,2013,26(12):3739.

[5] 左晓伟. 光纤复接器CMOS集成电路设计[M]. 南京:东南大学出版社,2007.

[6] 夏宇闻. Verilog数字系统设计教程(第2版)[M].北京:北京航空航天大学出版社,2008.(收稿日期:20160317)